### Sub-picosecond event timing new techniques & first results

Petr Panek, Ivan Prochazka\*

presented at ILRS Fall Meeting 2007, Grasse, France, September 25-27, 2007

Institute of Photonics and Electronics, Academy of Sciences of the Czech Republic, \* Czech Technical University in Prague Prague, Czech Republic

#### New timing principle theory by Petr Panek US Patent, 2005

**Petr Pánek** was born in Rakovník, Czech Republic, in 1957. He received the M.Sc. and Ph.D. degrees in electrical engineering from the Czech Technical University, Prague, Czech Republic, in 1982 and 1988, respectively.

From 1986 to 1988 he was with Aeronautical Research and Test Institute, Prague. In 1988 he joined Mesit, Uherské Hradiště, and since 1993 he has been with Dicom, Uherské Hradiště as a Senior Research Engineer responsible for positioning and timing systems. Since 2004 he is

also a scientist at the Institute of Radio Engineering and Electronics, Academy of Sciences of the Czech Republic, Prague. His current research interests are accurate time transfer and time interval measurement.

# Design Goals

- Sub picosecond event timing device

- Based on novel timing principle (P.Panek)

- Employing new technologies (ultrafast logic, "no ground", SAW filters,..)

- Self calibrating device no adjustment or calibration needed ever

- Space version possible (low mass, low power,..?)

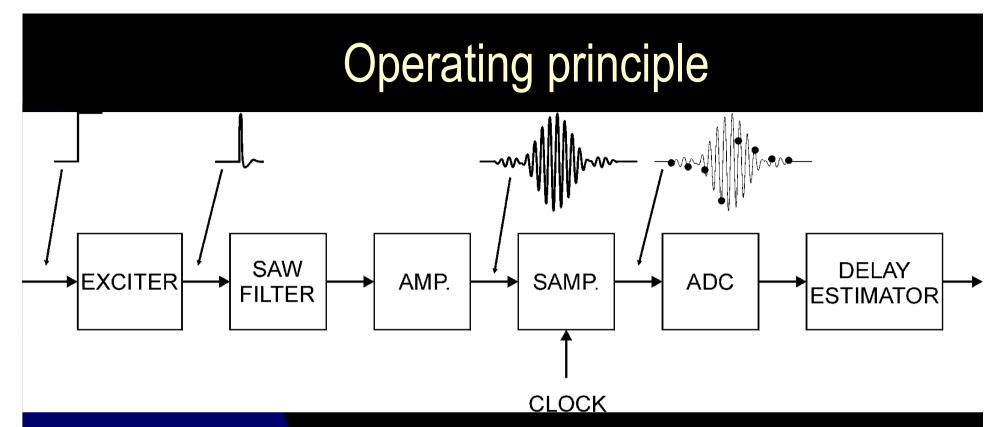

- The entire time measurement is carried out in a FREQUENCY DOMAIN

- The time-interpolator is realized by the Surface Acoustic Wave SAW filter

- The SAW filter output is sampled & digitized synchronously with the clock

- The resulting time / epoch is computed using the reverse FFT

#### Popis algoritmu:

1. Meze intervalu, na němž hledáme maximum, položíme

$s_1=-2,\,s_2=2\;$  a počáteční odhads=0 .

2. Určíme velikost korelace v bodě $\,s_1$

$$r_{1} = \left| \sum_{k=1}^{31} R(k) \exp\left(jks_{1}\frac{2\pi}{64}\right) \right|.$$

Výpočet provedeme následujícím způsobem:  $C_1(k) = \cos(ks_1\pi/32), S_1(k) = \sin(ks_1\pi/32), k = 1,...,31,$   $\operatorname{Re}[a_1] = \sum_{k=1}^{31} (\operatorname{Re}[R(k)] \cdot C_1(k) - \operatorname{Im}[R(k)] \cdot S_1(k)),$  $\operatorname{Im}[a_1] = \sum_{k=1}^{31} (\operatorname{Re}[R(k)] \cdot S_1(k) + \operatorname{Im}[R(k)] \cdot C_1(k)),$

$r_1 = \sqrt{\operatorname{Re}[a_1]^2 + \operatorname{Im}[a_1]^2}$ .

3. Určíme velikost korelace v bodě $\,s_2$

$$r_2 = \left| \sum_{k=1}^{31} R(k) \exp\left(jks_2 \frac{2\pi}{64}\right) \right|.$$

Výpočet provedeme následujícím způsobem:  $C_2(k) = \cos(ks_2\pi/32), S_2(k) = \sin(ks_2\pi/32), k = 1,...,31$ ,  $\operatorname{Re}[a_2] = \sum_{k=1}^{31} (\operatorname{Re}[R(k)] \cdot C_2(k) - \operatorname{Im}[R(k)] \cdot S_2(k))),$   $\operatorname{Im}[a_2] = \sum_{k=1}^{31} (\operatorname{Re}[R(k)] \cdot S_2(k) + \operatorname{Im}[R(k)] \cdot C_2(k))),$   $r_2 = \sqrt{\operatorname{Re}[a_2]^2 + \operatorname{Im}[a_2]^2}.$ 4. Určíme velikost korelace v bodě *s*

$$r = \left| \sum_{k=1}^{31} R(k) \exp\left( jks \frac{2\pi}{64} \right) \right|.$$

# Data processing

- Purpose converting the sampled and digitized wavefronts data into epochs

- Recursive ("selflearning") algorithm dedicated for repeated measurements

- The device self-calibration is included

- Complicated algorithm consisting of a numer of compex double precision arrays manipulation, multiple FFT etc.

- See attached list for ~ 10% of the description <sup>(2)</sup>

- High CPU and data volume requirements Time consuming, repetition rate limit <sup>®</sup>

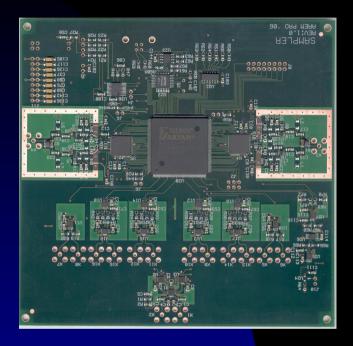

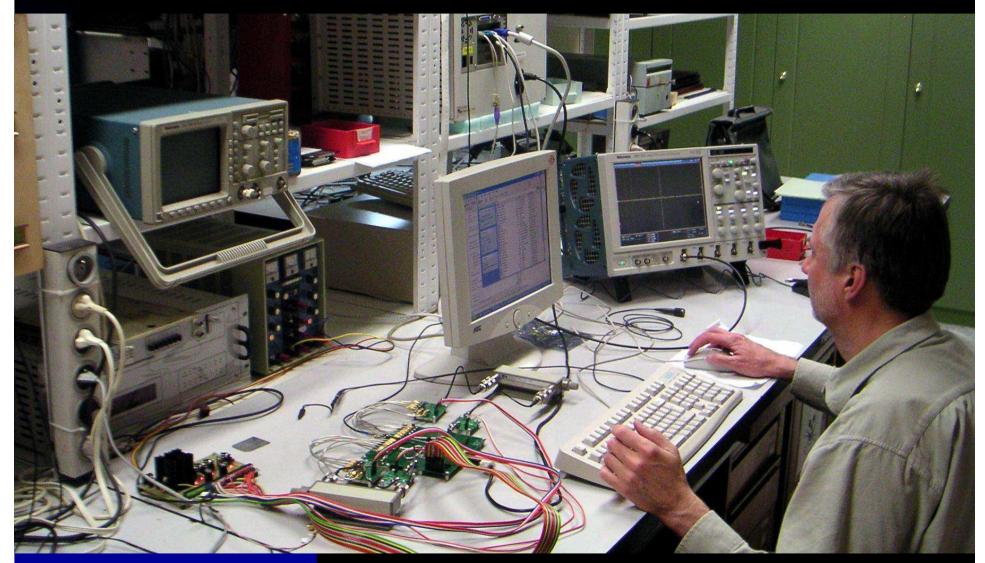

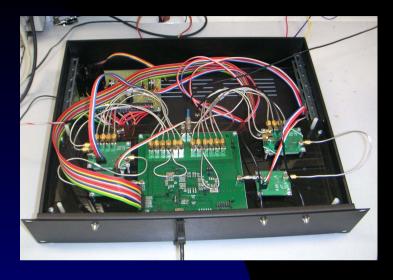

### Device design

- Based on theoretical papers by P.Panek, submitted to IEEE 2004-5

- Selected optimal combination of SAW filter central frequency, bandwidth, ...

- Based entirely on commercial components (2005)

- The clock reference 200 MHz Frequency Module designed and constructed by J.Kolbl and P.Sperber, Univ. of Deggendorf, 2005

- On the input stage employed the fastest available components,

- The device designed as modular, two channel event timer to enable independent modules modification and upgrade

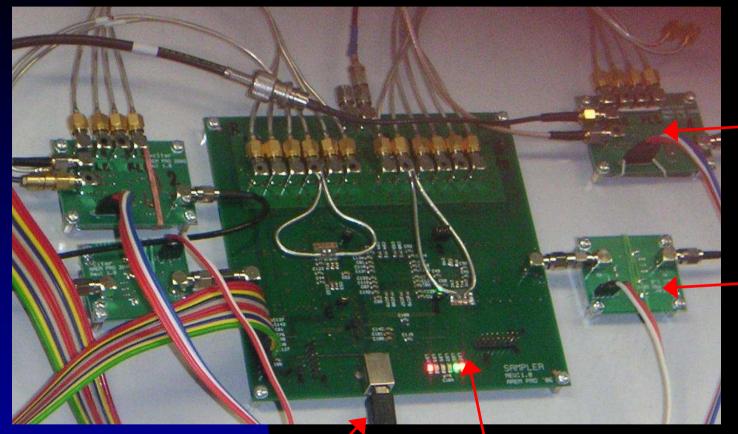

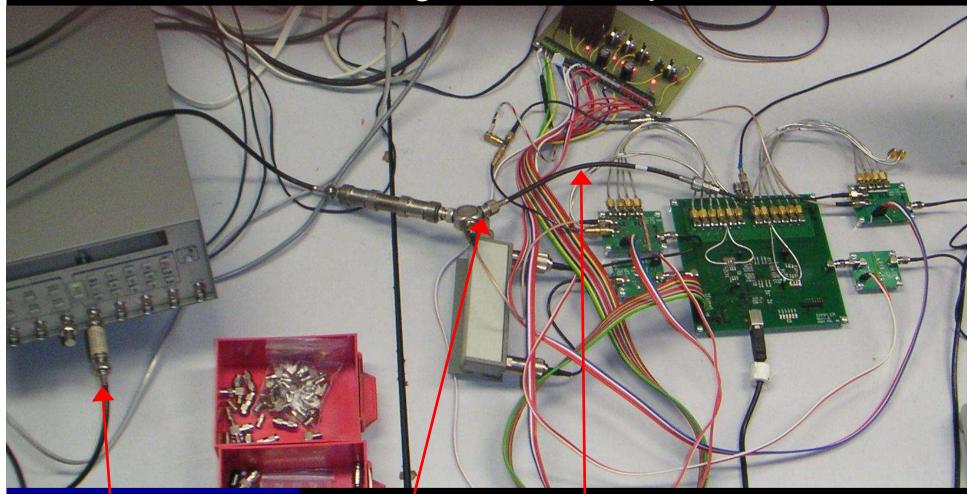

#### **Device construction** Event timer in operational configuration

#### Exciter

#### SAW filter

#### USB 2

#### Sampler and AD converter

### Technology challenges

- PCB design Advaced PCB design SW crashed due to board complexity <sup>(3)</sup>

- Equal signal path delay requirement (PCB + cable + PCB) < 10 ps (!!)</li>

- On board micro-strip ps delay lines

- Sub mm cable length tolerances (!!)

- Soldering of some SMD chips

#### 200MHz clock source J.Kolbl and P.Sperber, Univ. of Deggendorf

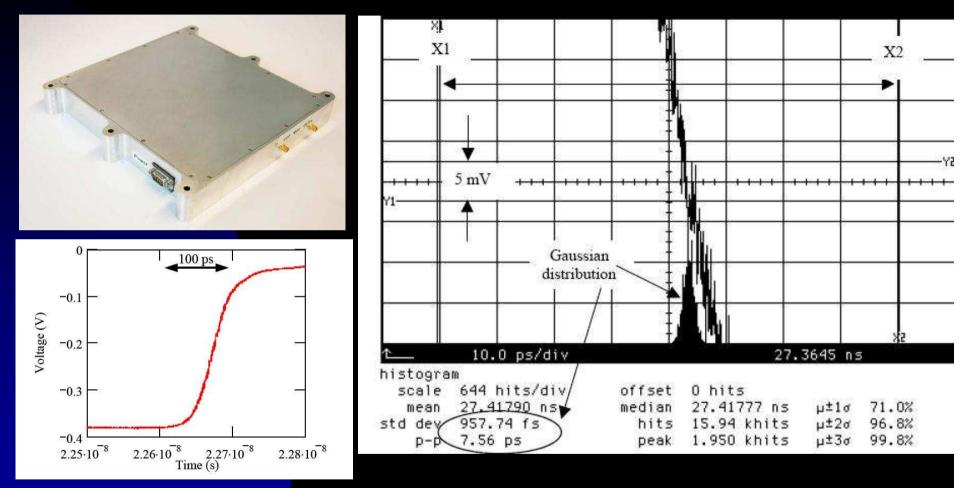

Risetime < 40 ps

Clock jitter << 1 psec

### **Device construction**

| Random error budget - individual contributors |                  |

|-----------------------------------------------|------------------|

|                                               | rms ps / channel |

| Noise of excitation                           | 0.78 ps          |

| <ul> <li>Noise of amplifiers</li> </ul>       | 0.29 ps          |

| Quantization                                  | negligible       |

| Clock and sampling jitter                     | 0.30 ps          |

| Aliasing                                      | 0.35 ps          |

| Resulting root sum square                     | 0.95 ps rms / ch |

|                                               |                  |

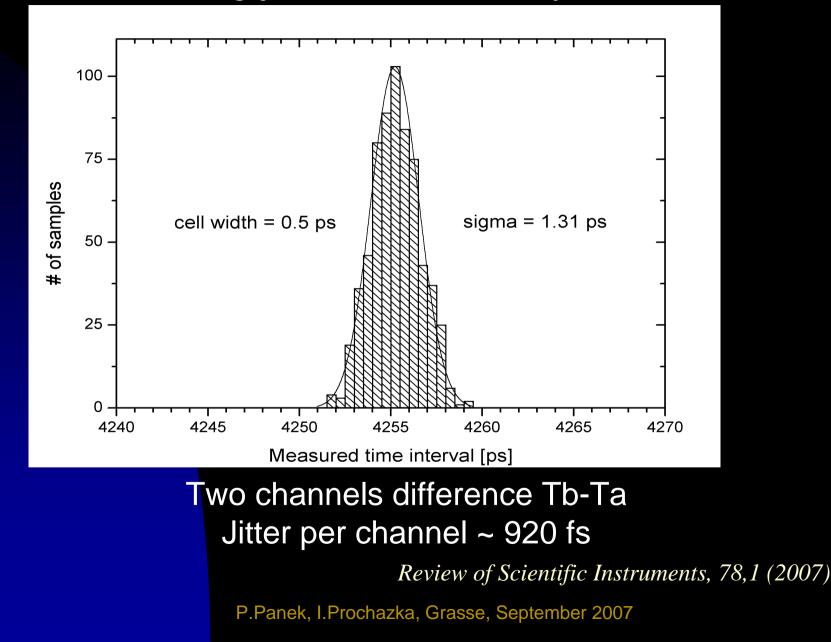

### Timing jitter - cable delay test

# Timing tests set up

#### Pulse generator

Pulse divider delay cable

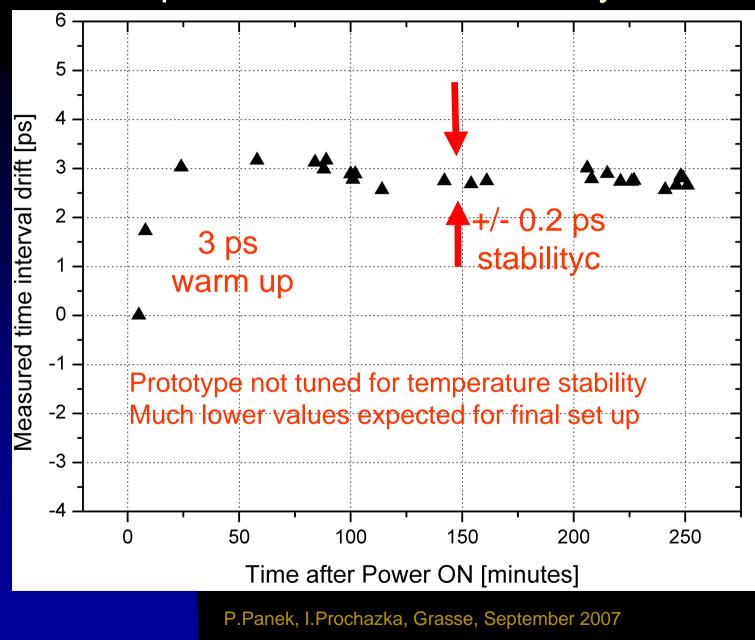

### Temperature drift - cable delay test

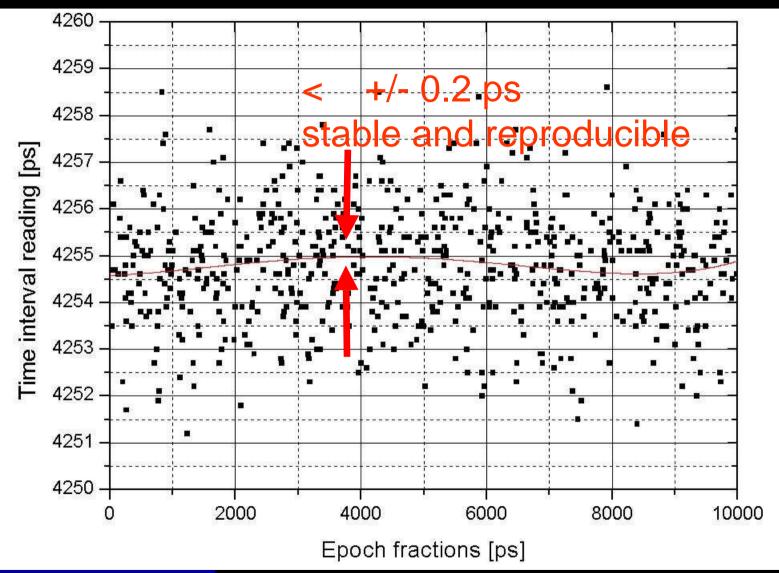

### Timing linearity

## Epoch timing device

- Epoch timing system, Two independent channels

- Inputs

#### NIM

- **Jitter**

- Non-linearity

- Stability

- Power

- Interface

- Repetition rate 10 Hz max

- 0.9 ps / ch < 0.2 ps

- < +/- 0.2 ps

- < 15 Watts

- USB

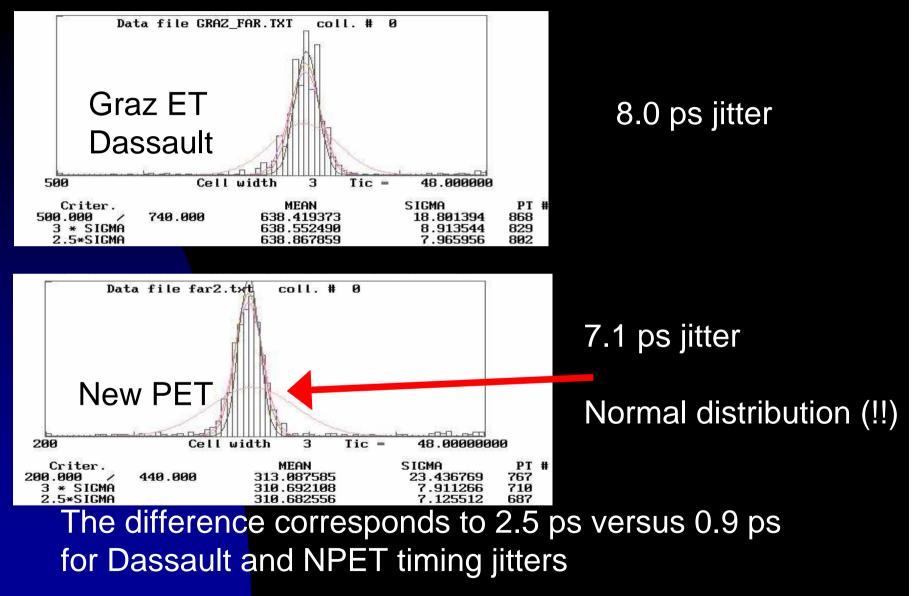

### SLR tests in Graz, 4.3 km ground target

# Summary

- GOOD NEWS

- Sub picosecond event timing device is existing

- jitter < 1 ps / channel</p>

- non-linearity, stability < 0.2 ps</p>

- further improvement expected ③

- The device is low power, compact, reliable

- The theoretical repetition rate limit is ~ 100 kHz ③

- BAD NEWS

- The data processing is time consuming, maximum rep. rate is limited, 100 Hz expected soon

- new approaches are needed for kHz systems

# Conclusion

- Sub picosecond event timing device is existing

- Novel timing principle (P.Panek) verified for the first time

- New technologies appreciated

- Self calibrating device no adjustment or calibration needed ever

- Space version seems to be possible

- Looking for applications ③